TDM over Packet (TDMoP)

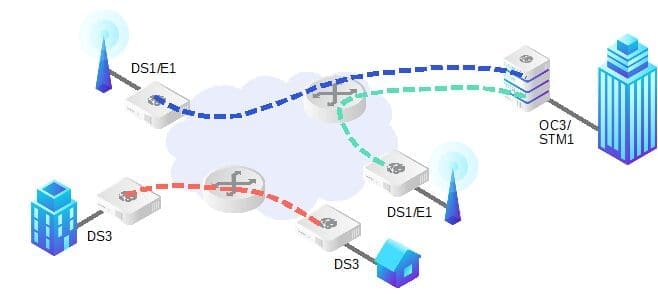

One of the main challenges in today’s telecom network designs is the smooth migration from a TDM based network to a packet based network.

A key driver for this change is to create a consolidated network that uses packet technology in the core backbone, the metro and the access network.

This single network could provide major commercial benefits with reduced capital (CAPEX) and operational (OPEX) expenditure, while retaining the recurring revenues from mission critical legacy TDM services. Application of TDM over Packet via Circuit Emulation Services allows a smooth migration and cost effective path for Communication Service Providers. Instead of using fixed bandwidth TDM links per individual end-service, the TDM traffic is packetized and aggregated with other TDM or IP traffic onto a single network.

Applications

- Mobile backhaul systems

- Legacy enterprise voice equipment with PABX

- Wholesale SONET/SDH transport

- TDM services in government or utility networks

AimValley Expertise

AimValley provides various FPGA based solutions for TDM over Packet applications. These are used in our equipment designs and available as building blocks for customers that develop TDM system solutions.

Generic Features

- Support for E1/T1, T3 and SONET/SDH, including several levels of channelization

- SAToP, CESoPSN and CEP modes compliant with IETF and MEF standards

- TDM channels can be configured independently for adaptive, differential or re-timing clock recovery

- Each channel may operate at a different clock rate

- Jitter/Wander performance exceeding ITU-T standards

- Integrated framers enable performance and fault monitoring, test pattern insert and loopback

- Configurable Ethernet, VLAN, IP/UDP and MPLS packet headers

- Dual GigE interface with optional protection

- Ideally prepared for new protocols or standards evolution due to FPGA based design

- Evaluation system for early demonstration and performance testing

AimValley proven track record

Our TDM to Packet expertise is successfully deployed in numerous product designs across many customers and their equipment. Millions of pseudowires are installed in Telecom networks worldwide using our TDM Smart SFP solutions. These are offered as easy to install plug-and-play configurations, or provided as fully managed and tightly integrated ports in customer network equipment.

Our integration and verification test teams use a wide array of test and measurement equipment for TDM protocols, synchronization and jitter/wander performance and packet network impairment generators to ensure compliance with all Telecom, synchronization, and packet network standards. Read more on TDM network migration.

Example Configurations

16 channel T1/E1

The 16 channel TDM over Packet configuration implements Circuit Emulation Services Interworking Functions (CES IWF) for DS1/E1 TDM channels.

The FPGA based solution integrates all functions for compact and cost-effective TDM transport applications such as wireless backhaul systems:

- DS1/E1 framers

- TDMoP interworking function

- Configurable clock recovery

- Packet header processing

Channelized SONET/SDH

This configuration implements CES IWF for a fully channelized OC-12 or STM-4 capacity. Each of the 336 DS1 or 252 E1 channels embedded on the line interface are processed individually to provide a high density Gateway between TDM over SONET/SDH and TDM over packet.

The FPGA based solution integrates all functions for SONT/SDH to packet gateway applications and access modernization systems:

- SONET/SDH line interfaces with 1+1 APS protection

- VT-1.5/VC-12 mappers

- DS1/E1 framers

- TDMoP interworking function

- Configurable clock recovery

- Packet header processing

Mixed interface configuration

This configuration supports TDM over packet for a channelized OC-3 or STM-1 interface and 16 additional physical DS1/E1 ports. Each of the physical or embedded DS1 or E1 channels is processed individually to provide a versatile TDMoP Gateway.

The FPGA based solutions integrates all functions for TDM transport gateway applications such as wireless backhaul systems:

- SONET/SDH line interfaces with 1+1 APS protection

- VT-1.5/VC-12 mappers

- DS1/E1 framers

- TDMoP interworking function

- Configurable clock recovery

- Packet header processing

The examples listed above are the most popular configurations in wireless backhaul and access modernization projects. Our library of functional building blocks supports virtually all legacy TDM interface rates, fractional and sub-channels, multiplexing and protocols such as: Nx64k, DS3, M13 mux, STS1/VC4 CEP and clear channel SONET/SDH/OTN over Packet. Due to the FPGA based architecture, the amount of channels and the aggregate bandwidth can be customized to meet exact target requirements. Furthermore, FPGAs enable further integration, including system level synchronization, hardware assisted hit-less protection switching and extended packet processing with OAM support, or other differentiating and customer unique value-add functionality.